# UNIT I

### INTRODUCTION TO MOS TRANSISTOR

## **Basic MOSFET Structure**

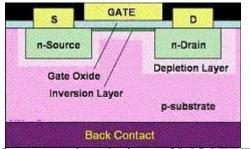

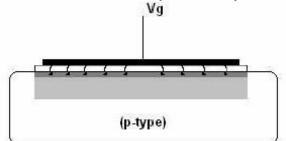

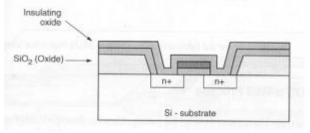

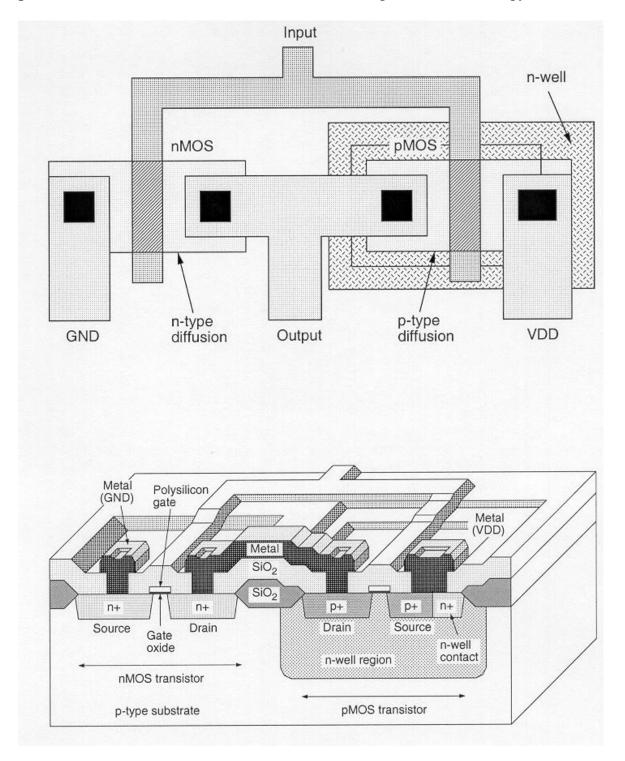

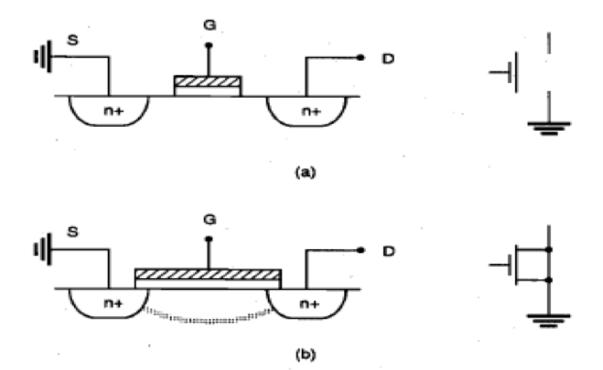

The cross-sectional and top/bottom view of MOSFET are as in figures 1 and 2 given below :

# MOSFET

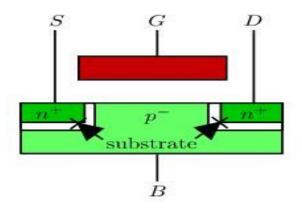

It consists of a **source** and a **drain**, two highly conducting n-type semiconductor regions which are separated from the p-type substrate by reverse-biased p-n diodes. A metal or poly crystalline gate covers the region between the source and drain, but is isolated from the semiconductor by the **gate oxide**.

# **Types of MOSFET**

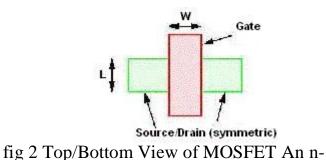

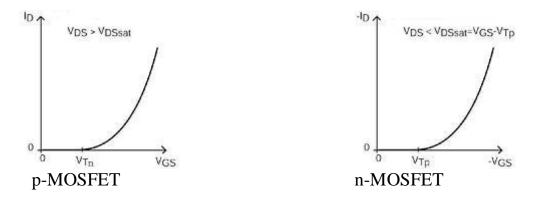

MOSFETs are divided into two types viz. **p-MOSFET** and **n-MOSFET** depending upon its type of source and drain.

The combination of a **n-MOSFET** and a **p-MOSFET** is called **cMOSFET** which is the mostly used as MOSFET transistor. We will look at it in more detail later.

### **MOSFET I-V Modelling**

We are interested in finding the outputcharacteristics () and the transfer charcteristics of the MOSFET. In other words, we can find out both if we can formulate a mathematical equation of the form:

$$\mathbf{v}_{OS} = \mathbf{f}(\mathbf{v}_{OST} \mathbf{v}_{GS})$$

We can say that voltage level specifications and the material parameters cannot be altered by designers. So the only tools in the designer's hands with which he/she can improve the performance of the device are its dimensions, W and L In fact, the most important parameter in the device simulations is ratio of W and L.

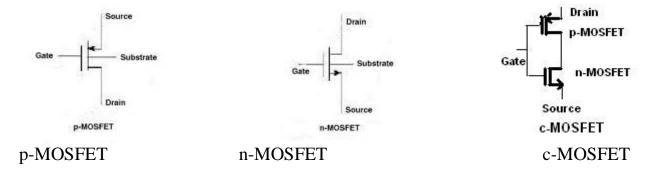

The equations governing the **output** and **transfer** characteristics of an **n**-MOSFET and **p**-MOSFET are :

$$\mathbf{p} \cdot \mathbf{MOSFET:} \begin{array}{l} I_{SD} = \begin{cases} 0.5\beta_p [2(v_{SG} - |V_{Tp}|)V_{SD} - V_{SD}^2] & \text{Linear} \\ 0.5\beta_p [V_{SG} - |V_{Tp}|]^2 & \text{Saturation} \end{cases}$$

n-MOSFET:

$$I_{DS} = \begin{cases} 0.5\beta_n [2(V_{GS} - |V_{Tn}|)V_{DS} - V_{DS}^2] & \text{Linear} \\ 0.5\beta_n [V_{GS} - |V_{Tn}|]^2 & \text{Saturation} \end{cases}$$

The **output** characteristics plotted for few fixed values of for **p**-MOSFET and **n**-MOSFET are shown next :

The **transfer** characteristics of both **p**-MOSFET and **n**-MOSFET are plotted for a fixed value of as shown next :

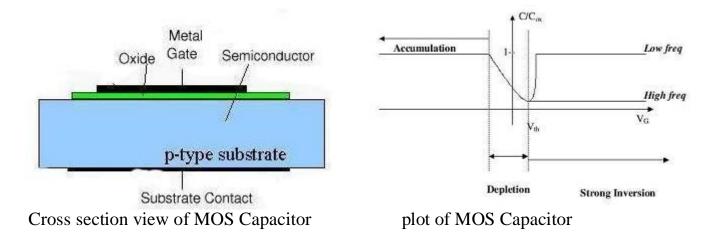

### C-V Characteristics of a MOS Capacitor

As we have seen earlier, there is an oxide layer below Gate terminal. Since oxide is a very good insulator, it contributes to an oxide capacitance in the circuit. Normally, the capacitance value of a capacitor doesn't change with values of voltage applied across its terminals. However, this is not the case with MOS capacitor. We find that the capacitance of MOS capacitor changes its value with the variation in Gate voltage. This is because application of gate voltage results in the band bending of silicon substrate and hence variation in charge concentration at **Si-SiO2** interface. Also we can see that the curve splits into two (reason will be explained later), after a certain voltage, depending upon the frequency (high or low) of AC voltage applied at the gate. This voltage is called the threshold voltage(**Vth**) of MOS capacitor.

### Modes of operation

Depending upon the value of gate voltage applied, the MOS capacitor works in three modes :

Accumulation mode (grey layer - strong hole concentration)

Depletion Mode (light grey layer – depletion region)

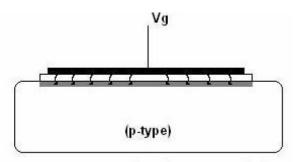

- **1. Accumulation:** In this mode, there is accumulation of holes (assuming n-MOSFET) at the Si-SiO2 interface. All the field lines emanating from the gate terminate on this layer giving an effective dielectric thickness as the oxide thickness. In this mode, Vg <0

- **2. Depletion:** As we move from negative to positive gate voltages the holes at the interface are repelled and pushed back into the bulk leaving a depleted layer. This layer counters the positive charge on the gate and keeps increasing till the gate voltage is below threshold voltage. we see a larger effective dielectric length and hence a lower capacitance.

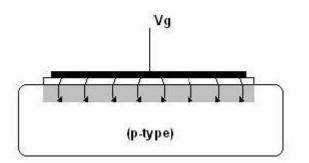

- **3. Strong Inversion:** When Vg crosses threshold voltage, the increase in depletion region width stops and charge on layer is countered by mobile electrons at Si-SiO2 interface. This is called inversion because the mobile charges are opposite to the type of charges found in substrate. In this case the inversion layer is formed by the electrons. Field lines hence terminate on this layer thereby reducing the effective dielectric thickness

Strong Inversion mode (grey layer - strongelectron concentration, light grey - depletion region)

### Threshold voltage

It is that gate voltage at which the surface band bending is twice  $\varphi_F = \frac{kT}{q} ln(\frac{N_A}{n_i})$

We know that the depth of depletion region for  $\varphi_s$  is between 0 and  $2\varphi_F$  and is given by,

$$x_d = \sqrt{\frac{2 \in_{\rm s} \varphi_{\rm s}}{q N_{\rm a}}}$$

Charge in depletion region at  $\varphi_s - 2\varphi_F$  is given by  $Q_D = -qN_a x_{dmax}$  where

$$X_{dmax} = \sqrt{\frac{2 \in (2\varphi_F)}{qN_a}}$$

Beyond threshold, the total charge QD in the seminconductor has to balance the charge on gate electrode,  $Q_s$  i.e.  $Q_s = (Q_I + Q_D)$  where we define the charge in the inversion layer as a quantity which needs to be determined.

This leads to following expression for gate voltage-

$$V_{GS} = V_{FB} + \varphi_S + \frac{Q_S}{C_{ox}} = V_{FB} + \varphi_S - \frac{(Q_I + Q_D)}{C_{ox}}$$

In case of depletion, there in no inversion layer charge, so  $\mathbf{Q_i} = \mathbf{0}$ , i.e. gate voltage becomes

$$V_{GS} = V_{FB} + \varphi_S - \frac{Q_D}{C_{ox}} = V_{FB} + \varphi_S + \frac{2\sqrt{qN_a \in \varphi_F}}{C_{ox}} \text{ for } 0 \le \varphi_S \le 2\varphi_F$$

but in case of inversion, the gate voltage will be given by :

The second term in second equality of last expression states our basic assumption, namely that any change in gate voltage beyond the threshold requires a change in inversion layer charge. Also from the same expression, we obtain threshold voltage as :

$$V_{F} = V_{FB} + 2\varphi_{F} + \frac{2\sqrt{qN_{a}} \in_{s} \varphi_{F}}{C_{ox}}$$

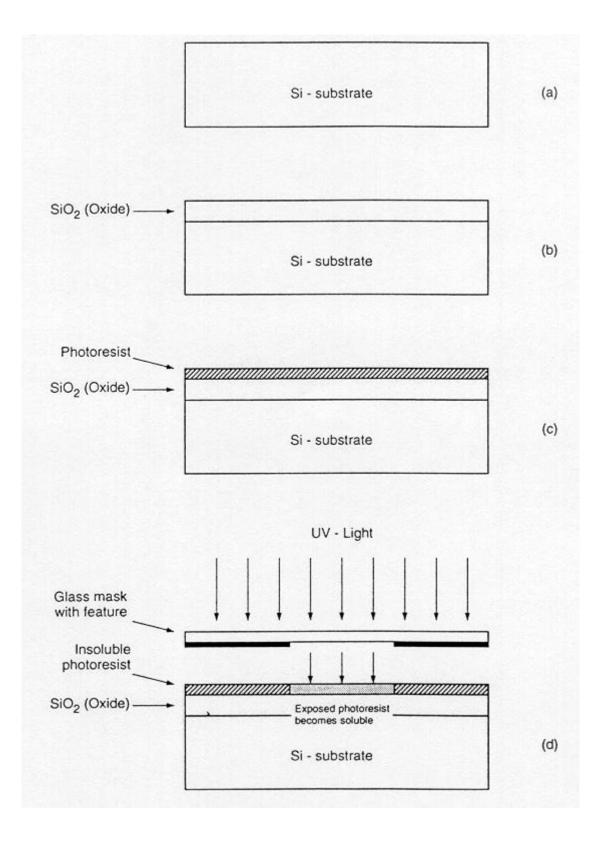

#### **MOS Fabrication:**

#### Step1:

Processing is carried on single crystal silicon of high purity on which required P impurities are introduced as crystal is grown. Such wafers are about 75 to 150 mm in diameter and 0.4 mm thick and they are doped with say boron to impurity concentration of 10 to power 15/cm3 to 10 to the power 16 /cm3.

## **Step 2 :**

A layer of silicon di oxide (SiO2) typically 1 micrometer thick is grown all over the surface of the wafer to protect the surface, acts as a barrier to the dopant during processing, and provide a generally insulating substrate on to which other layers may be deposited and patterned.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | and the second |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| The second se                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Si - substrate                                                                                                   |

| and the second se | or - substrate                                                                                                   |

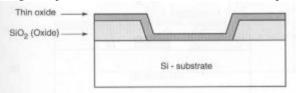

# Step 3:

The surface is now covered with the photo resist which is deposited onto the wafer and spun to an even distribution of the required thickness.

| iiO <sub>2</sub> (Oxide) | •              |

|--------------------------|----------------|

|                          | Si - substrate |

# Step 4:

The photo resist layer is then exposed to ultraviolet light through masking which defines those regions into which diffusion is to take place together with transistor channels. Assume, for example, that those areas exposed to uv radiations are polymerized (hardened), but that the areas required for diffusion are shielded by the mask and remain unaffected.

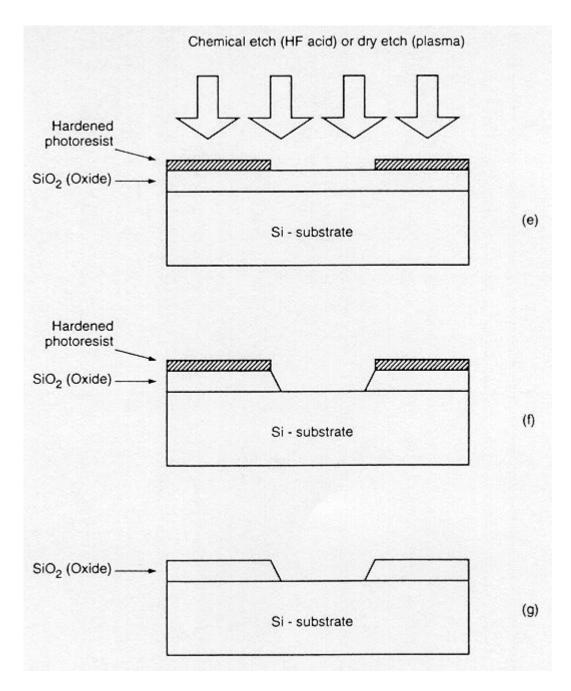

# Step 5:

These areas are subsequently readily etched away together with the underlying silicon di oxide so that the wafer surface is exposed in the window defined by the mask.

|                                                     | Chemical etch (HF acid | d) or dry etch (plasma) |

|-----------------------------------------------------|------------------------|-------------------------|

| Hardened<br>photoresist<br>SIO <sub>2</sub> (Oxide) | 11.                    | 11                      |

|                                                     | Si - subst             | irate                   |

# Step 6:

The remaining photo resist is removed and a thin layer of SiO2 (0.1 micro m typical) is grown over the entire chip surface and then poly silicon is deposited on the top of this to form the gate structure. The polysilicon layer consists of heavily doped polysilicon deposited by chemical vapour deposition (CVD). In the fabrication of fine pattern devices, precise control of thickness, impurity concentration, and resistivity is necessary

# Step 7:

Further photo resist coating and masking allows the poly silicon to be patterned and then the thin oxide is removed to expose areas into which n-type impurities are to be diffused to form the source and drain. Diffusion is achieved by heating the wafer to a high temperature and passing a gas containing the desired n-type impurity.

Note: The poly silicon with underlying thin oxide and the thick oxide acts as mask during diffusion the process is self aligning.

Step 8:

Thick oxide (SiO2) is grown over all again and is then masked with photo resist and etched to expose selected areas of the poly silicon gate and the drain and source areas where connections are to be made. (contacts cut)

### Step 9:

The whole chip then has metal (aluminium) deposited over its surface to a thickness typically of 1 micro m. This metal layer is then masked and etched to form the required interconnection pattern.

# **BODY EFFECT:**

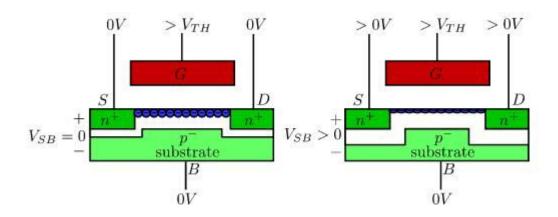

Transistor is a 4-terminal device. Gate, drain and source are the 3 terminals that are used to control the transistor, but the bulk or body, if not properly biased, may put the transistor inoperable.

The pn junctions defined by source-bulk and drain-bulk, which are basically two diodes, must be reverse-biased to stop them from leaking current from the source/drain to the substrate. That means that the source potential must always be equal or greater than the bulk potential. Since drain voltage is always greater or equal than source voltage, we don't even consider the drain-bulk junction.

When VS>VB, the depletion width of the pn junction increases That makes it more difficult to create a channel with the same VGS, effectively reducing the channel depth. In order to return to the same channel depth, VGS needs to increase accordingly. The body effect can be seen as a change in threshold voltage

## **Channel Length modulation**.

This in MOSFET is caused by the increase in depletion layer width at the drain as the drain voltage is increased. This leads to a shorter channel length (reduced by  $\Delta L$ ) and increased drain current. When the channel length of MOSFET is decreased and MOSFET is operated beyond channel pinch-off, the relative importance of pinchoff length  $\Delta L$  with respect to physical length is increased. This effect can be included in saturation current as :

$$\begin{aligned} \mathbf{I}_{DSSat}' &= \frac{\mathbf{I}_{DSSat}}{1 - \frac{\Delta L}{L}} \\ \mathbf{I}_{DSSat} &= \mu_n \frac{W}{L} C_{ox} \frac{(V_{GS} - V_T)^2}{2} (1 + \lambda V_{DS}) \end{aligned}$$

Here  $\mathbf{\lambda}$  is called channel length modulation coefficient

# **CMOS Fabrication:**

CMOS fabrication can be accomplished using either of the three technologies:

- N-well/P-well technologies

- Twin well technology

- Silicon On Insulator (SOI)

## **Twin Well Technology**

Using twin well technology, we can optimise NMOS and PMOS transistors separately. This means that transistor parameters such as threshold voltage, body effect and the channel transconductance of both types of transistors can be tuned independenly.

n+ or p+ substrate, with a lightly doped epitaxial layer on top, forms the starting material for this technology. The n-well and pwell are formed on this epitaxial layer which forms the actual substrate. The dopant concentrations can be carefully optimized to produce the desired device characterisitcs because two independent doping steps are performed to create the well regions.

The conventional n-well CMOS process suffers from, among other effects, the problem of unbalanced drain parasitics since the doping density of the well region typically being about one order of magnitude higher than the substrate. This problem is absent in the twin-tub process.

### Silicon on Insulator (SOI)

To improve process characteristics such as speed and latch-up susceptibility, technologists have sought to use an insulating substrate instead of silicon as the substrate material.

Completely isolated NMOS and PMOS transistors can be created virtually side by side on an insulating substrate (eg. sapphire) by using the SOI CMOS technology.

This technology offers advantages in the form of higher integration density (because of the absence of well regions), complete avoidance of the latch-up problem, and lower parasitic capacitances compared to the conventional n-well or twin-tub CMOS processes.

But this technology comes with the disadvantage of higher cost than the standard n-well CMOS process. Yet the improvements of device performance and the absence of latch- up problems can justify its use, especially in deep submicron devices.

## N-well Technology

In this discussion we will concentrate on the well established n-well CMOS fabrication technology, which requires that both nchannel and p-channel transistors be built on the same chip substrate. To accomodate this, special regions are created with a semiconductor type opposite to the substrate type. The regions thus formed are called wells or tubs. In an n-type substrate, we can create a p-well or alternatively, an n-well is created in a p-type substrate. We present here a simple n-well CMOS fabrication technology, in which the NMOS transistor is created in the p-type substrate, and the PMOS in the n-well, which is built-in into the p-type substrate.

Historically, fabrication started with p-well technology but now it has been completely shifted to n-well technology. The main reason for this is that, "n-well sheet resistance can be made lower than p-well sheet resistance" (electrons are more mobile than holes).

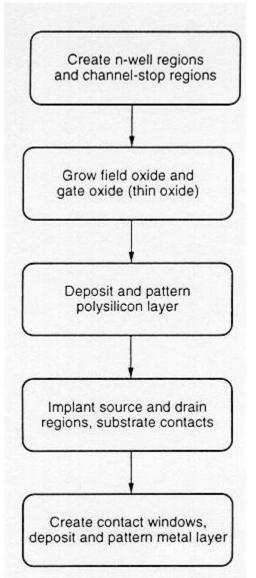

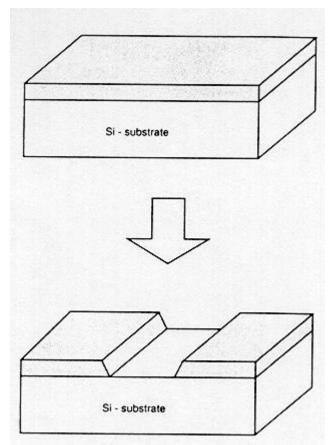

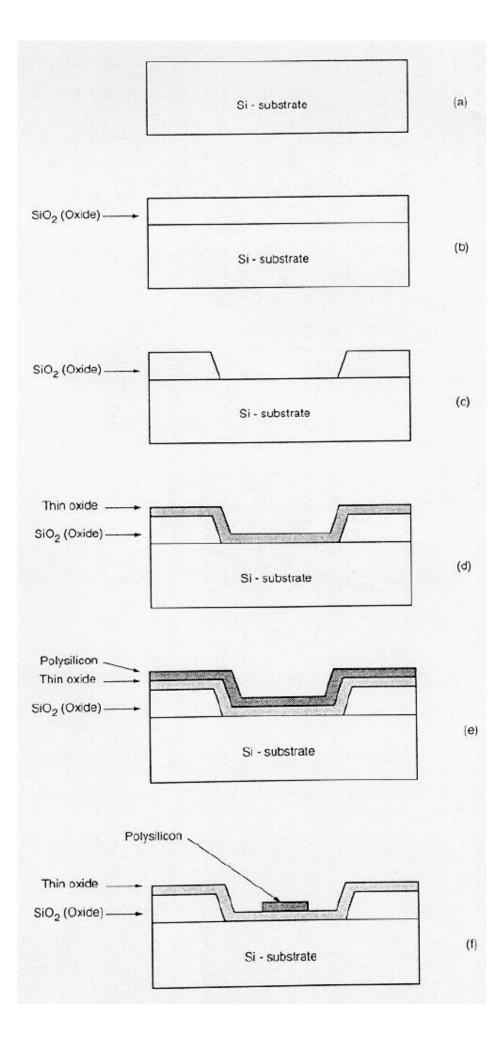

The simplified process sequence (shown in Figure 12.41) for the fabrication of CMOS integrated circuits on a p-type silicon substrate is as follows:

- N-well regions are created for PMOS transistors, by impurity implantation into the substrate.

- This is followed by the growth of a thick oxide in the regions surround the NMOS and PMOS active regions.

- The thin gate oxide is subsequently grown on the surface through thermal oxidation.

- After this n+ and p+ regions (source, drain and channel-stop implants) are created.

- The metallization step (creation of metal interconnects) forms the final step in this process.

Simplified Process Sequence For Fabrication Of CMOS ICs

The integrated circuit may be viewed as a set of patterned layers of doped silicon, polysilicon, metal and insulating silicon dioxide, since each processing step requires that certain areas are defined on chip by appropriate masks. A layer is patterned before the next layer of material is applied on the chip. A process, called lithography, is used to transfer a pattern to a layer. This must be repeated for every layer, using a different mask, since each layer has its own distinct requirements.

We illustrate the fabrication steps involved in patterning silicon dioxide through optical lithography, which shows the lithographic sequences.

Process steps required for patterning of silicon dioxide

First an oxide layer is created on the substrate with thermal oxidation of the silicon surface. This oxide surface is then covered with a layer of photoresist. Photoresist is a light-sensitive, acid-resistant organic polymer which is initially insoluble in the developing solution. On exposure to ultraviolet (UV) light, the exposed areas become soluble which can be etched away by etching solvents. Some areas on the surface are covered with a mask during exposure to selectively expose the photoresist. On exposure to UV light, the masked areas are shielded whereas those areas which are not shielded become soluble.

There are two types of photoresists, positive and negative photoresist. Positive photoresist is initially insoluble, but becomes soluble after exposure to UV light, where as negative photoresist is initially soluble but becomes insoluble (hardened) after exposure to UV light. The process sequence described uses positive photoresist.

Negative photoresists are more sensitive to light, but their photolithographic resolution is not as high as that of the positive photoresists. Hence, the use of negative photoresists is less common in manufacturing high-density integrated circuits.

The unexposed portions of the photoresist can be removed by a solvent after the UV exposure step. The silicon dioxide regions not covered by the hardened photoresist is etched away by using a chemical solvent (HF acid) or dry etch (plasma etch) process. On completion of this step, we are left with an oxide window which reaches down to the silicon surface. Another solvent is used to strip away the remaining photoresist from the silicon dioxide surface. The patterned silicon dioxide feature is shown in Figure 12.43

The result of single photolithographic patterning sequence on silicon dioxide

The sequence of process steps illustrated in detail actually accomplishes a single pattern transfer onto the silicon dioxide surface. The fabrication of semiconductor devices requires several such pattern transfers to be performed on silicon dioxide, polysilicon, and metal. The basic patterning process used in all fabrication steps, however, is quite similar to the one described earlier. Also note that for accurate generation of high- density patterns required in submicron devices, electron beam (E-beam) lithography is used instead of optical lithography.

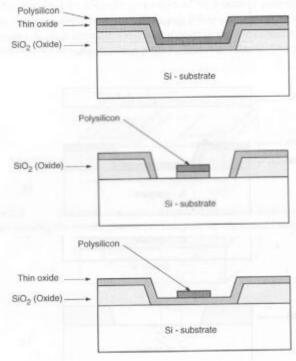

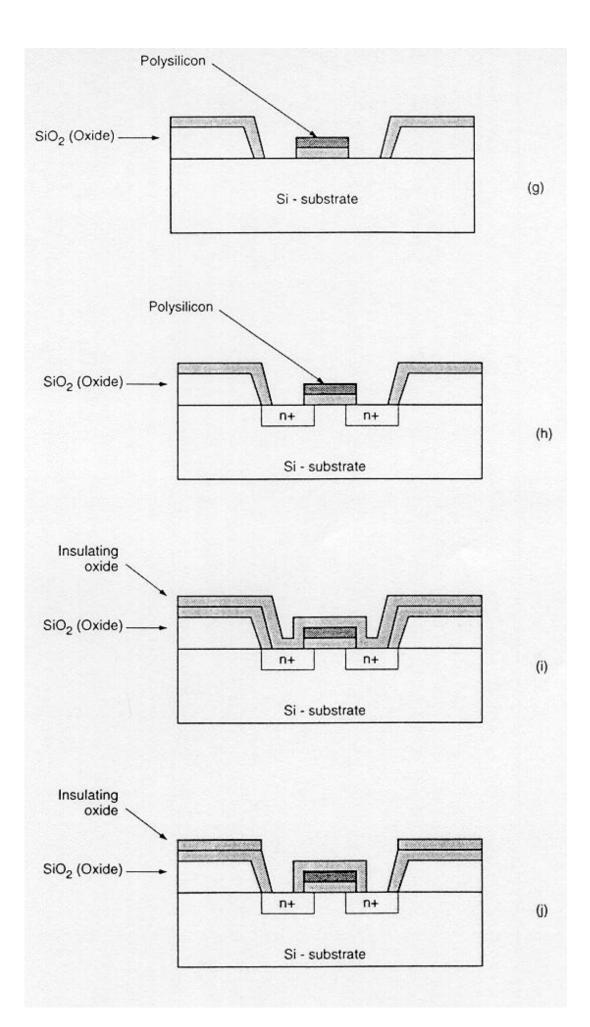

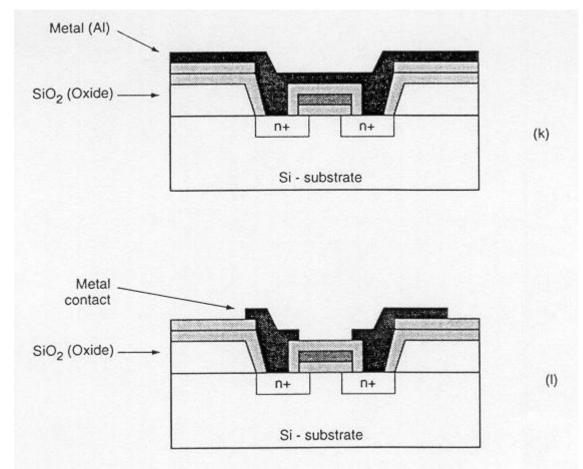

In this section, we will examine the main processing steps involved in fabrication of an nchannel MOS transistor on a p-type silicon substrate. The first step of the process is the oxidation of the silicon substrate which creates a relatively thick silicon dioxide layer on the surface. This oxide layer is called field oxide The field oxide is then selectively etched to expose the silicon surface on which the transistor will be created. After this the surface is covered with a thin, high-quality oxide layer. This oxide layer will form the gate oxide of the MOS transistor Then a polysilicon layer is deposited on the thin oxide Polysilicon is used as both a gate electrode material for MOS transistors as well as an interconnect medium in silicon integrated circuits. The resistivity of polysilicon, which is usually high, is reduced by doping it with impurity atoms.

Deposition is followed by patterning and etching of polysilicon layer to form the interconnects and the MOS transistor gates The thin gate oxide not masked by polysilicon is also etched away exposing the bare silicon surface. The drain and source junctions are to be formed Diffusion or ion implantation is used to dope the entire silicon surface with a high concentration of impurities (in this case donor atoms to produce n-type doping). Two n-type regions (source and drain junctions) in the p-type substrate as doping penetrates the exposed areas of the silicon surface. The penetration of impurity doping into the polysilicon reduces its resistivity. The polysilicon gate is patterned before the doping and it precisely defines the location of the channel region and hence, the location of the source and drain regions. Hence this process is called a self-aligning process.

The entire surface is again covered with an insulating layer of silicon dioxide after the source and drain regions are completed Next contact windows for the source and drain are patterned into the oxide layer. Interconnects are formed by evaporating aluminium on the surface which is followed by patterning and etching of the metal layer A second or third layer of metallic interconnect can also be added after adding another oxide layer, cutting (via) holes, depositing and patterning the metal.

Process flow for the fabrication of an n-type MOSFET on p-type silicon

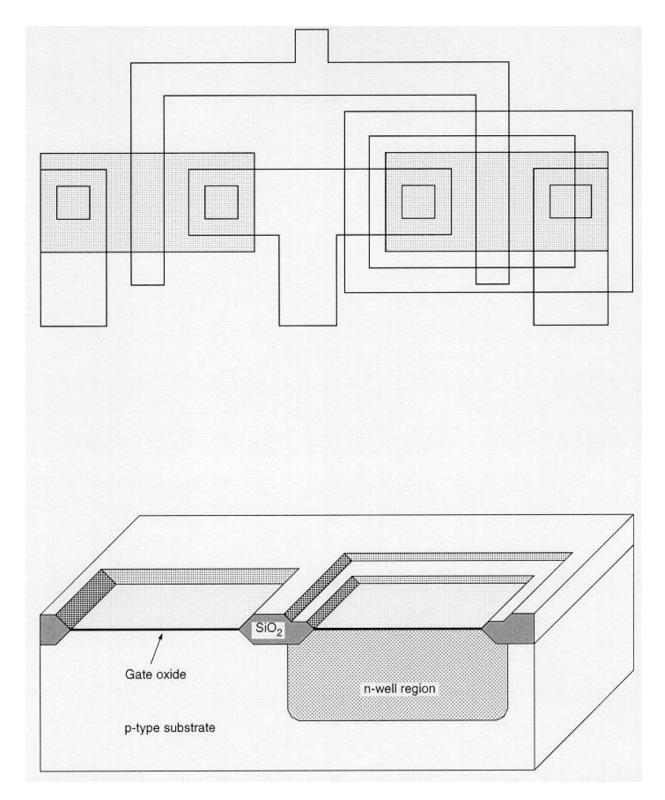

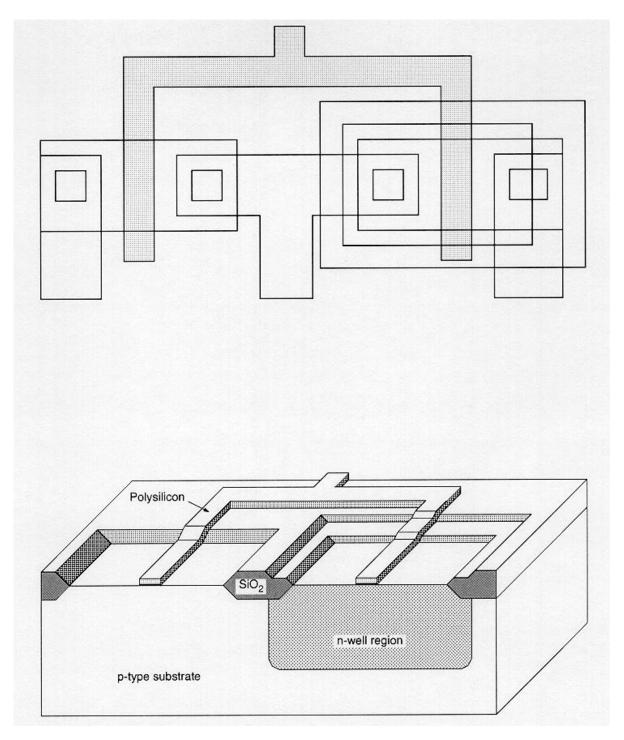

We now return to the generalized fabrication sequence of n-well CMOS integrated circuits. The following figures illustrate some of the important process steps of the fabrication of a CMOS inverter by a top view of the lithographic masks and a cross- sectional view of the relevant areas.

The n-well CMOS process starts with a moderately doped (with impurity concentration typically less than 1015 cm-3) p-type silicon substrate. Then, an initial oxide layer is grown on the entire surface. The first lithographic mask defines the n-well region. Donor atoms, usually phosphorus, are implanted through this window in the oxide. Once the n- well is created, the active areas of the nMOS and pMOS transistors can be defined

The creation of the n-well region is followed by the growth of a thick field oxide in the areas surrounding the transistor active regions, and a thin gate oxide on top of the active regions. The two most important critical fabrication parameters are the thickness and quality of the gate oxide. These strongly affect the operational characteristics of the MOS transistor, as well as its long-term stability.

Chemical vapor deposition (CVD) is used for deposition of polysilicon layer and patterned by dry (plasma) etching. The resulting polysilicon lines function as the gate electrodes of

the nMOS and the pMOS transistors and their interconnects. The polysilicon gates also act as self-aligned masks for source and drain implantations.

The n+ and p+ regions are implanted into the substrate and into the n-well using a set of two masks. Ohmic contacts to the substrate and to the n-well are also implanted in this process step.

CVD is again used to deposit and insulating silicon dioxide layer over the entire wafer. After this the contacts are defined and etched away exposing the silicon or polysilicon contact windows. These contact windows are essential to complete the circuit interconnections using the metal layer, which is patterned in the next step.

Metal (aluminum) is deposited over the entire chip surface using metal evaporation, and the metal lines are patterned through etching. Since the wafer surface is non-planar, the quality and the integrity of the metal lines created in this step are very critical and are ultimately essential for circuit reliability.

The composite layout and the resulting cross-sectional view of the chip, showing one nMOS and one pMOS transistor (built-in nwell), the polysilicon and metal interconnections. The final step is to deposit the passivation layer (for protection) over the chip, except for wire-bonding pad areas.

This completes the fabrication of the CMOS inverter using n-well technology.

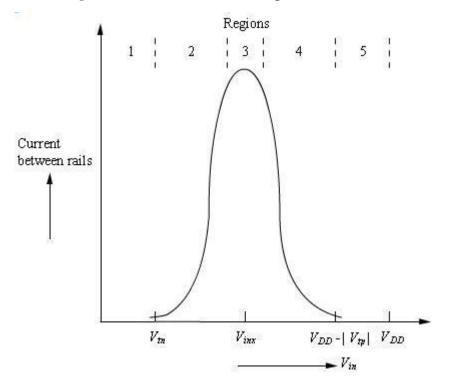

#### **DC Characteristics of CMOS:**

Let  $V_{tn}$  and  $V_{tp}$  denote the threshold voltages of the *n* and *p*-devices respectively. The following voltages at the gate and the drain of the two devices (relative to their respective sources) are all referred with respect to the ground (or  $V_{SS}$ ), which is the substrate voltage of the *n*-device, namely

$V_{gsn} = V_{in}$ ,  $V_{dsn} = V_{out}$ ,  $V_{gsp} = V_{in} - V_{DD}$ , and  $V_{dsp} = V_{out} - V_{DD}$ .

The voltage transfer characteristic of the CMOS inverter is now derived with reference to the following five regions of operation :

**Region 1** : the input voltage is in the range  $0 \le V_{in} < V_{in}$ . In this condition, the *n* -transistor is off, while the *p* -transistor is in linear region (as  $-V_{DD} < V_{gap} < -V_{DD} + V_{in}$ ).

No actual current flows until  $V_{in}$  crosses  $V_{tn}$ , as may be seen from Figure 2.11. The operating point of the *p*-transistor moves from higher to lower values of currents in linear zone.

**Region 2** : the input voltage is in the range  $V_{in} \leq V_{in} < V_{in}$ . The upper limit of  $V_{in}$  is  $V_{inv}$ , the *logic threshold voltage* of the inverter. The logic threshold voltage or the *switching point voltage* of an inverter denotes the boundary of "logic 1" and "logic 0". It is the output voltage at which  $V_{in} = V_{out}$ . In this region, the *n*-transistor moves into saturation, while the *p*-transistor remains in linear region. The total current through the inverter increases, and the output voltage tends to drop fast.

**Region 3** : In this region,  $V_{1} \approx V_{1} \approx V_{1}$ . Both the transistors are in saturation, the drain current attains a maximum value, and the output voltage falls rapidly. The inverter exhibits gain. But this region is

inherently unstable. As both the transistors are in saturation, equating their currents, one gets  $(as^{V_{grad}} = V_{inv}, V_{grad} = V_{inv}, V_{DD}).$

$$\frac{1}{2}\beta_{x}\left(V_{ixy} - V_{ix}\right)^{2} = \frac{1}{2}\beta_{y}\left(V_{ixy} - V_{DD} - V_{iy}\right)^{2}$$

where  $\beta = K \frac{W}{L}$  and  $K = \frac{\varepsilon_{inv} \varepsilon_0 \mu}{D}$ . Solving for the logic threshold voltage  $V_{inv}$ , one gets

$$V_{pq} = \frac{V_{DD} + V_{qy} + V_{tx} \left(\frac{\beta_{tx}}{\beta_{y}}\right)^{1/2}}{1 + \left(\frac{\beta_{tx}}{\beta_{y}}\right)^{1/2}}$$

Note that if  $\beta_n = \beta_p$  and  $V_{n} = -V_{n}$ , then  $V_{inv} = 0.5 V_{DD}$

**Region 4** : In this region,  $V_{in} < V_{in} \le V_{DD} - |V_{in}|$ . As the input voltage  $V_{in}$  is increased beyond  $V_{inv}$ , the *n*-transistor leaves saturation region and enters linear region, while the *p*-transistor continues in saturation. The magnitude of both the drain current and the output voltage drops.

**Region 5** : In this region,  $|V_{DD} - |V_{tp}| \le V_{in} \le V_{DD}$ . At this point, the *p*-transistor is turned off, and the *n*-transistor is in linear region, drawing a small current, which falls to zero as  $V_{in}$  increases beyond  $V_{DD}$  -/  $V_{tp}$ /, since the *p*-transistor turns off the current path. The output in this region

## UNIT II

#### MOS CIRCUITS DESIGN PROCESS AND CMOS LOGIC GATES

### **Types of Design Rules**

The design rules primary address two issues:

- 1. The geometrical reproduction of features that can be reproduced by the maskmaking and lithographical process ,and

- 2. The interaction between different layers.

There are primarily two approaches in describing the design rules.

- 1. Linear scaling is possible only over a limited range of dimensions.

- 2. Scalable design rules are conservative .This results in over dimensioned and less dense design.

- 3. This rule is not used in real life.

## 1. Scalable Design Rules (e.g. SCMOS, $\lambda$ -based design rules):

In this approach, all rules are defined in terms of a single parameter  $\lambda$ . The rules are so chosen that a design can be easily ported over a cross section of industrial process ,making the layout portable .Scaling can be easily done by simply changing the value of.

The key disadvantages of this approach are:

### 2. Absolute Design Rules (e.g. µ-based design rules ) :

In this approach, the design rules are expressed in absolute dimensions (e.g.

$0.75\mu$ m) and therefore can exploit the features of a given process to a maximum degree. Here, scaling and porting is more demanding, and has to be performed either manually or using CAD tools .Also, these rules tend to be more complex especially for deep submicron.

The fundamental unity in the definition of a set of design rules is the minimum line width .It stands for the minimum mask dimension that can be safely transferred to the semiconductor material .Even for the same minimum dimension, design rules tend to differ from company to company, and from process to process. Now, CAD tools allow designs to migrate between compatible processes.

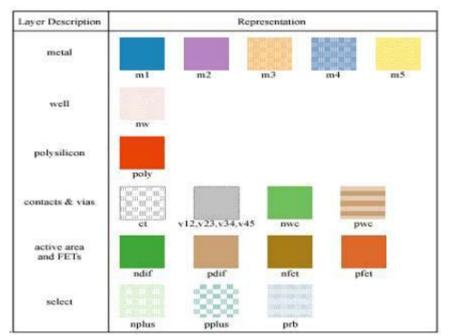

# Layer Representations

With increase of complexity in the CMOS processes, the visualization of all the mask levels that are used in the actual fabrication process becomes inhibited. The layer concept translates these masks to a set of conceptual layout levels that are easier to visualize by the circuit designer. From the designer's viewpoint, all CMOS designs have the following entities:

- Two different substrates and/or wells: which are p-type for NMOS and n-type for PMOS.

- Diffusion regions (p+ and n+): which defines the area where transistors can be formed. These regions are also called **active areas**. Diffusion of an inverse type is needed to implement contacts to the well or to substrate. These are called **select regions**.

- Transistor gate electrodes : Polysilicon layer

- Metal interconnect layers

- Interlayer contacts and via layers.

The layers for typical CMOS processes are represented in various figures in terms of:

- A color scheme (Mead-Conway colors).

- Other color schemes designed to differentiate CMOS structures.

- Varying stipple patterns

- Varying line styles

Mead Conway Color coding for layers.

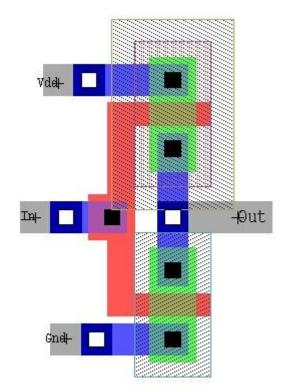

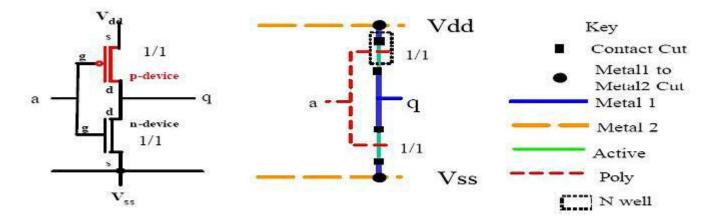

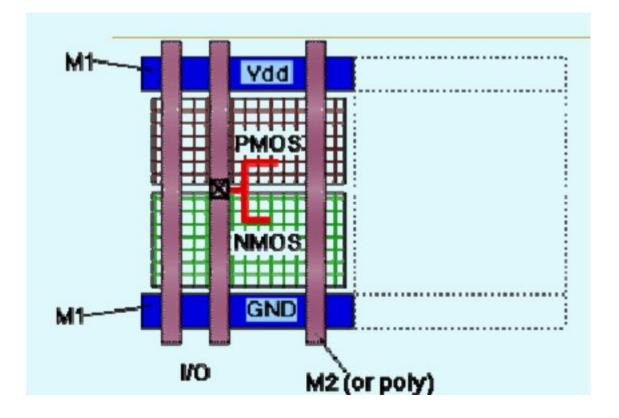

An example of layer representations for CMOS inverter using above design rules is shown below-

CMOS Inverter Layout Figure

## Stick Diagrams

Another popular method of symbolic design is "**Sticks**" layout. In this, the designer draws a freehand sketch of a layout, using colored lines to represent the various process layers such as diffusion, metal and polysilicon .Where polysilicon crosses diffusion, transistors are created and where metal wires join diffusion or polysilicon, contacts are formed.

This notation indicates only the relative positioning of the various design components. The absolute coordinates of these elements are determined automatically by the editor using a compactor. The compactor translates the design rules into a set of constraints on the component positions, and solve a constrained optimization problem that attempts to minimize the area or cost function.

The advantage of this symbolic approach is that the designer does not have to worry about design rules, because the compactor ensures that the final layout is physically correct. The disadvantage of the symbolic approach is that the outcome of the compaction phase is often unpredictable. The resulting layout can be less dense than what is obtained with the manual approach. In addition, it does not show exact placement, transistor sizes, wire lengths, wire widths, tub boundaries.

For example, stick diagram for CMOS Inverter is shown below.

Stick Diagram of a CMOS Inverter

# LAYOUT DIAGRAM

Layout rules are used to prepare the photo mask used in the fabrication of integrated circuits. The rules provide the necessary communication link between the circuit designer and process engineer. Design rules represent the best possible compromise between performance and yield.

The design rules primarily address two issues -

1. The geometrical reproductions of features that can be reproduced by mask making and lithographical processes.

2. Interaction between different layers

Design rules can be specified by different approaches

- 1.  $\lambda$ -based design rules

- 2. µ-based design rules

As  $\lambda$ -based layout design rules were originally devised to simplify the industry- standard  $\mu$ -based design rules and to allow scaling capability for various processes. It must be emphasized, however, that most of the submicron CMOS process design rules do not lend themselves to straightforward linear scaling. The use of  $\lambda$ -based design rules must therefore be handled with caution in sub-micron geometries.

## λ-based Design Rules

Features of  $\lambda$ -based Design Rules:  $\lambda$ -based Design Rules have the following features-

- $\lambda$  is the size of a minimum feature

- All the dimensions are specified in integer multiple of  $\lambda$ .

- Specifying  $\lambda$  particularizes the scalable rules.

- Parasitic are generally not specified in  $\lambda$  units

- These rules specify geometry of masks, which will provide reasonable yields

# Guidelines for using $\lambda$ -based Design Rules:

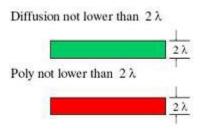

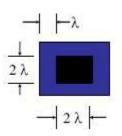

As, Minimum line width of poly is  $2\lambda$  & Minimum line width of diffusion is  $2\lambda$

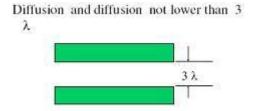

As Minimum distance between two diffusion layers  $3\lambda$

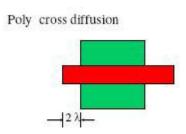

As It is necessary for the poly to completely cross active, other wise the transistor that has been created crossing of diffusion and poly, will be shorted by diffused path of source and drain.

## **Contact cut on metal**

Contact window will be of  $2\lambda$  by  $2\lambda$  that is minimum feature size while metal deposition is of  $4\lambda$  by  $4\lambda$  for reliable contacts.

# In Metal

Two metal wires have  $3\lambda$  distance between them to overcome capacitance coupling and high frequency coupling. Metal wires width can be as large as possible to decrease resistance.

## **Buttering contact**

Buttering contact is used to make poly and silicon contact. Window's original width is  $4\lambda$ , but on overlapping width is  $2\lambda$ .

So actual contact area is  $6\lambda$  by  $4\lambda$ .

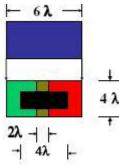

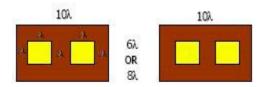

The **distance between two wells** depends on the well potentials as shown above. The reason for 8l is that if both wells are at same high potential then the depletion region between them may touch each other causing punch-through. The reason for 6l is that if both wells are at different potentials then depletion region of one well will be smaller, so both depletion region will not touch each other so 6l will be good enough.

6λ. For both wells at different potential

8λ. For both wells at same potential

The active region has length  $10\lambda$  which is distributed over the followings-

- $2\lambda$  for source diffusion

- $2\lambda$  for drain diffusion

- $2\lambda$  for channel length

- $2\lambda$  for source side encroachment

- $2\lambda$  for drain side encroachment

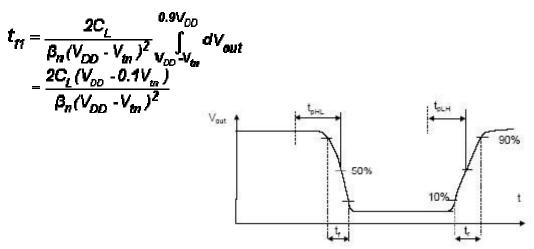

## **Basic Definitions in Delay:**

Before calculating the propagation delay of CMOS Inverter, we will define some basic terms-

- Switching speed limited by time taken to charge and discharge, CL.

- Rise time, tr: waveform to rise from 10% to 90% of its steady state value

- Fall time tf: 90% to 10% of steady state value

- Delay time, td: time difference between input transition (50%) and 50% output level

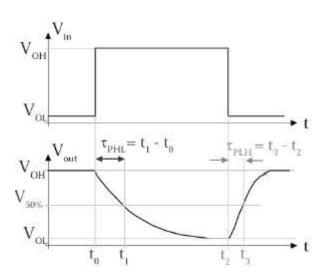

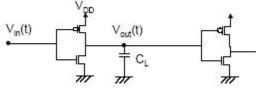

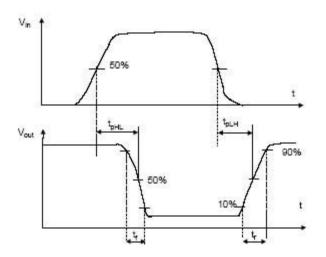

### Propagation delay graph

The propagation delay **tp** of a gate defines how quickly it responds to a change at its inputs, it expresses the delay experienced by a signal when passing through a gate. It is measured between the 50% transition points of the input and output waveforms as shown in the figure 16.1 for an inverting gate. The <sup>T</sup>pHL defines the response time of the gate for a low to high output transition, while <sup>T</sup>pHL refers to a high to low transition. The propagation delay <sup>T</sup>p as the average of the two  $\tau_p = (\tau_{oLH} + \tau_{oHL})/2$

#### **Quick Estimates:**

We will give an example of how to calculate quick estimate. From fig, we can write following equations.

Example CMOS Inverter Circuit

Propagation Delay of above MOS circuit

From figure, when Vin = 0 the capacitor CL charges through the PMOS, and when Vin = 5 the capacitor discharges through the N-MOS. The capacitor current is –

$$C_L \frac{dV}{dt} = I_{dsn} = |I_{dsp}|$$

From this the delay times can be derived as

$$\int dt = \int \frac{C_L}{i_{ds}} dV$$

The expressions for the propagation delays as denoted in the figure (16.22) can be easily seen to be

$$\begin{aligned} \tau_{PHL} &= \frac{C_{Load} \Delta V_{HL}}{I_{avg,HL}} - \frac{C_{Load} (V_{OH} - V_{50\%})}{I_{avg,HL}} & \& \tau_{PLH} = \frac{C_{Load} \Delta V_{LH}}{I_{avg,LH}} - \frac{C_{Load} (V_{50\%} - V_{OL})}{I_{avg,HL}} \\ \text{where } I_{avg,HL} \& I_{avg,LH} & \text{are defined as -} \\ I_{avg,HL} &= \frac{1}{2} [I_{C} (V_{in} = V_{OH}, V_{out} = V_{OH}) + I_{C} (V_{in} = V_{OH}, V_{out} = V_{50\%})] \\ I_{avg,LH} &= \frac{1}{2} [I_{C} (V_{in} = V_{OL}, V_{out} = V_{OL}) + I_{C} (V_{in} = V_{OL}, V_{out} = V_{50\%})] \end{aligned}$$

**Rise and Fall Times**

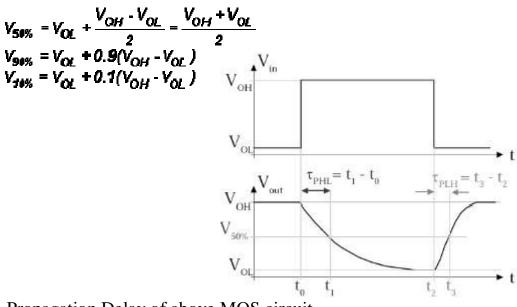

trjectory of n-transistor operating point

Above Figure shows the trajectory of the n-transistor operating point as the input voltage, Vin(t), changes from 0V to VDD. Initially, the end-device is cutt-off and the load capacitor is charged to VDD. This illustrated by X1 on the characteristic curve. Application of a step voltage (VGS = VDD) at the input of the inverter changes the operating point to X2. From there onwards the trajectory moves on the VGS= VDD characteristic curve towards point X3 at the origin.

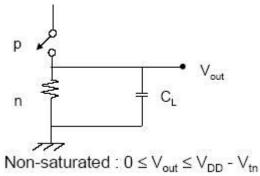

Thus it is evident that the fall time consists of two intervals:

1. tf1=period during which the capacitor voltage, Vout, drops from 0.9VDD to

## (VDD-Vtn)

2. tf2=period during which the capacitor voltage, Vout, drops from (VDD–Vtn) to

## 0.1VDD.

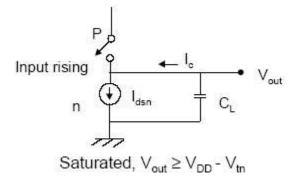

Equivalent circuit for showing behav. of tf1

Equivalent circuit for showing behav. of tf2

As we saw in last section, the delay periods can be derived using the general equation

$$\int dt = \int \frac{C_L}{i_{ds}} dV$$

while in saturation,

$$I_{dsn(sat)} = \frac{\beta_n}{2} (V_{in} - V_{in})^2$$

Integrating from t = t1, corresponding to **Vout=0.9 VDD**, to t = t2 corresponding to **Vout=(VDD-***V*tn) results in,

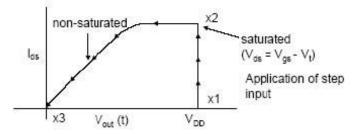

Rise and Fall time graph

When the n-device begins to operate in the linear region, the discharge current is no longer constant. The time **tf1** taken to discharge the capacitor voltage from (*V***DD**-*V***tn**) to *0.1V***DD** can be obtained as before. In linear region,

$$\begin{split} I_{dsn(linear)} &= -\beta_n [(V_{DD} - V_{tn}) V_{out} - V_{out}^2 / 2] \\ t_{r2} &= \frac{C_L}{\beta_n (V_{DD} - V_{tn})^2} \int_{V_{DD} - V_{tn}}^{0.1 V_{DD}} \frac{dV_{out}}{V_{out}^2} = \frac{C_L}{\beta_n (V_{DD} - V_{tn})} \ln \left(\frac{19V_{DD} - 20V_{tn}}{V_{DD}}\right) \\ &= \frac{C_L}{\beta_n V_{DD} (1 - n)} \ln (19 - 20n) \qquad \text{where } n = \frac{V_{tn}}{V_{DD}} \end{split}$$

Thus the complete term for the fall time is,

$$t_{f} = t_{f1} + t_{f2} = \frac{2C_{L}}{\beta_{n}V_{DD}(1-n)} \left[\frac{(n-0.1)}{(1-n)} + \frac{1}{2}\ln(19-20n)\right]$$

The fall time tf can be approximated as,

$$t_f \approx k_n \frac{C_L}{\beta_n V_{DD}}$$

$k_n = 3 - 4$  for  $V_{DD} = 3 - 5V$  and  $V_{tn} = 0.5 - 1V$

From this expression we can see that the delay is directly proportional to the load capacitance. Thus to achieve high speed circuits one has to minimize the load capacitance seen by a gate. Secondly it is inversely proportion to the supply voltage i.e. as the supply voltage is raised the delay time is reduced. Finally, the delay is proportional to the  $\beta n$  of the driving transistor so increasing the width of a transistor decreases the delay.

Due to the symmetry of the CMOS circuit the rise time can be similarly obtained as; For equally sized **n** and **p** transistors (where  $\beta n=2\beta p$ ) tf=tr

Thus the fall time is faster than the rise time primarily due to different carrier mobilites associated with the p and n devices thus if we want tf=tr we need to make  $\beta n/\beta p = 1$ . This implies that the channel width for the **p**-device must be increased to approximately 2 to 3 times that of the **n**-device.

The propagation delays if calculated as indicated before turn out to be,

$$\begin{aligned} \mathcal{T}_{PLH} &= \frac{C_L}{k_P \left( V_{DD} \cdot |V_{T0P}| \right)} \left[ \frac{2 |V_{T0P}|}{(V_{DD} \cdot |V_{T0P}|)} + \ln \left( \frac{4 \left( (V_{DD} \cdot |V_{T0P}|) \right)}{V_{DD}} \cdot 1 \right) \right] \\ \mathcal{T}_{PHL} &= \frac{C_L}{k_n \left( V_{DD} \cdot V_{T0n} \right)} \left[ \frac{2 V_{T0n}}{(V_{DD} \cdot V_{T0n})} + \ln \left( \frac{4 \left( (V_{DD} \cdot V_{T0n}) \right)}{V_{DD}} \cdot 1 \right) \right] \end{aligned}$$

Rise and Fall time graph of Output w.r.t Input

If we consider the rise time and fall time of the input signal as well, then

$$\begin{split} \mathcal{T}_{PLH(\text{actual})} &= \sqrt{(\mathcal{T}_{PLH})^2 + (t_f/2)^2} \\ \mathcal{T}_{PHL(\text{actual})} &= \sqrt{(\mathcal{T}_{PHL})^2 + (t_f/2)^2} \end{split}$$

These are the rms values for the propagation delays.

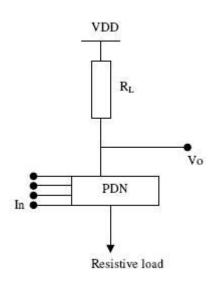

### **Ratioed Logic:**

Instead of combination of active pull down and pull up networks such a gate consists of an NMOS pull down network that realizes the logic function and a simple load device. For an inverter PDN is single NMOS transistor.

## Ratioed Logic Circuit

The load can be a passive device, such as a resistor or an active element as a transistor. Let us assume that both PDN and load can be represented as linearized resistors. The operation is as follows: For a low input signal the pull down network is off and the output is high by the load. When the input goes high the driver transistor turns on, and the resulting output voltage is determined by the resistive division between the impedances of pull down and load network:

## **VOL= RDVDD/(RD+RL)**

where  $\mathbf{R}D =$ pulldown n/w resistance,  $\mathbf{R}L =$ load resistance.

To keep the low noise margin high it is important to chose RL >>RD. This style of logic therefore called ratioed, because a careful **PDN** scaling of impedances (or transistor sizes) is required to obtain a workable gate. This is in contrast to the ratioless logic style as complementary CMOS, where the low and high level don't depend upon transistor sizes. As a satisfactory level we keep RL >=4RD. To achieve this, (W/L)D/(W/L)L > 4.

#### **Pass Transistor Logic**

The fundamental building block of nMOS dynamic logic circuit, consisting of an nMOS

pass transistor is shown in figure

Pass Transistor Logic Circuit

The pass transistor MP is driven by the periodic clock signal and acts as an access switch to either charge up or down the parasitic capacitance, Cx, depending on the input signal Vin. Thus there are 2 possible operations when the clock signal is active are the logic "1" transfer( charging up the capacitance Cx to logic high level) and the logic "0" transfer( charging down the capacitance Cx to a logic low level). In either case, the output of the depletion load of the nMOS inverter obviously assumes a logic low or high level, depending on the voltage Vx. The pass transistor MP provides the only current path to the intermediate capacitive node X. when clock signal becomes inactive (**clk=0**) the pass transistor ceases to conduct and the charge is stored in the parasitic capacitor Cx continues to determine the output level of the inverter. Logic "1" Transfer: Assume that the Vx = 0 initially. A logic "1"level is applied to the input terminal which corresponds to Vin=VOH=VDD. Now the clock signal at the gate of the pass transistor goes from 0 to VDD at t=0. It can be seen that the pass transistor starts to conduct and operate in saturation throughout this cycle since VDS=VGS. Consequently VDS> VGSVtn.

**Analysis:** The pass transistor operating in saturation region starts to charge up the capacitor **C**x, thus:

$$C_{X}(dV_{X}/dt) = (k_{n}/2)(V_{DD} - V_{X} - V_{tn})^{2} \Rightarrow \int_{0}^{t} dt = (2C_{X}/k_{n})\int_{0}^{V_{X}} dV_{X}/(V_{DD} - V_{X} - V_{tn})^{2}$$

So,  $t = (2C_{X}/k_{n})[1/(V_{DD} - V_{X} - V_{tn}) - 1/(V_{DD} - V_{tn})]$

The previous equation for Vx(t) can be solved as-

$$V_{x}(t) = (V_{DD} - V_{tn}) \frac{(k_{n}/2C_{x})(V_{DD} - V_{tn})t}{1 + (k_{n}/2C_{x})(V_{DD} - V_{tn})t}$$

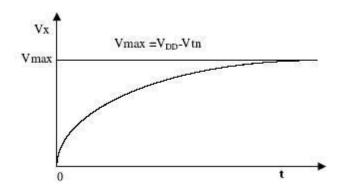

The variation of the node voltage Vx(t) is plotted as a function of time in fig. The voltage rises from its initial value of **0** and reaches **Vmax =VDD-Vtn** after a large time. The pass transistor will turn off when Vx = Vmax. Since **Vgs= Vtn**. Therefore **Vx** can never attain **VDD** during logic **1** transfer. Thus we can use buffering to overcome this problem.

Node Voltage Vx vs t

Logic "0" Transfer: Assume that the *V*x=1

Initially. A logic"0" level is applied to the input terminal which corresponds to *Vin=1*. Now the clock signal at the gate of the pass transistor goes from 0 to VDD at **t=0**. It can be seen that the pass transistor starts to conduct and operate in linear mode throughout this cycle and the drain current flows in the opposite direction to that of charge up.

Analysis: We can write -

$$-C_{x}(dV_{x}/dt) = (k_{n}/2)[(V_{DD} - V_{tn})V_{x} - V_{x}^{2}] \Rightarrow \int_{0}^{t} dt = -(C_{x}/k_{n})\int_{0}^{V_{x}} dV_{x}/[(V_{DD} - V_{tn})V_{x} - V_{x}^{2}]$$

So,  $t = (C_{x}/k_{n})\ln[2((V_{DD} - V_{tn}) - V_{x})/V_{x}]$

The above equation for Vx(t) can be solved as –

$$V_{x}(t) = \frac{2(V_{DD} - V_{tn})}{1 + e^{(k_{n}/C_{x})t}}$$

Plot of **Vx**(**t**) is shown in figure

Node Voltage Vx vs t

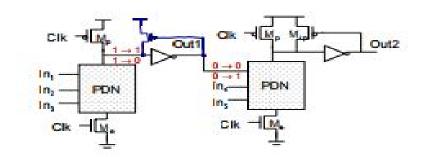

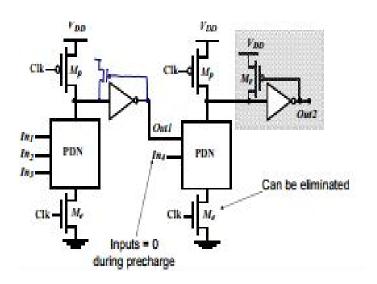

## **Dynamic Logic Circuits**

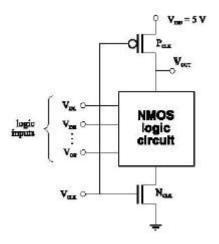

In case of static CMOS for a fan-in of **N**, **2N** transistors are required. In order to reduce this, various other design logics were used like pseudo-NMOS logic and pass transistor logic. However the static power consumption in these cases increased. An alternative to these design logics is **Dynamic logic**, which reduces the number of transistors at the same time keeps a check on the static power consumption.

Principle: A block diagram of a dynamic logic circuit is as shown in fig 19.31. This uses

NMOS block to implement its logic

The operation of this circuit can be explained in two modes.

- 1. Precharge

- 2. Evaluation

## **Dynamic CMOS Block Diagram**

In the precharge mode, the **CLK** input is at logic **0**. This forces the output to logic **1**, charging the load capacitance to **VDD**. Since the NMOS transistor **M1** is off the pulldown path is disabled. There is no static consumption in this case as there is no direct path between supply and ground.

In the evaluation mode, the **CLK** input is at logic **1**. Now the output depends on the PDN block. If there exists a path through PDN to ground (i.e. the PDN network is **ON**), the capacitor **CL** will discharge else it remains at logic **1**. As there exists only one path between the output node and a supply rail, which can only be ground, the load capacitor can discharge only once and if this happens, it cannot charge until the next precharge operation. Hence the inputs to the gate can make at most one transition during evaluation

#### DOMINO CMOS Block Diagram

#### Advantages of dynamic logic circuits:

1. As can be seen, the number of transistors required here are N+2 as compared to

2N in the Static CMOS circuits.

2. This circuit is still a ratioless circuit as in Static case. Hence, progressive sizing and ordering of the transistors in the PDN block is important.

3. As can be seen, the static power loss is negligible.

#### Disadvantages of dynamic logic circuits:

1. The penalty paid in such circuits is that the clock must run everywhere to each such block as shown in the diagram.

2. The major problem in such circuits is that the output node is at Vdd till the end of the precharge mode. Now if the **CLK** in the next block arrives earlier compared to the **CLK** in this block, or the PDN network in this block takes a longer time to evaluate its output, then the next block will start to evaluate using this erroneous value

The second part of the disadvantage can be eliminated by using **DOMINO CMOS** circuits which are as shown below.

As can be seen the output at the end of precharge is inverted by the inverter to logic 0. Thus the next block will not be evaluated till this output has been evaluated. As an ending point, it must be noted that this also has a disadvantage that since at each stage the output is inverted, the logic must be changed to accommodate this.

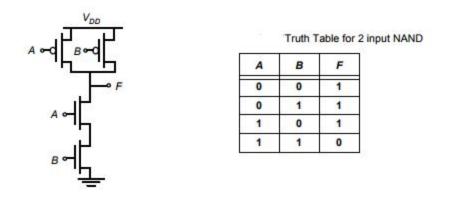

## STATIC CMOS LOGIC:

The most widely used logic style is static complementary CMOS. The static CMOS style is really an extension of the static CMOS inverter to multiple inputs. In review, the primary advantage of the CMOS structure is robustness (i.e, low sensitivity to noise), good performance, and low power consumption (with no static power consumption). As we will The complementary CMOS circuit style falls under a broad class of logic circuits called static circuits in which at every point in time (except during the switching transients), each gate output is connected to either VDD or Vss via a low-resistance path. Also, the outputs of the gates assume at all times the value of the Boolean function implemented by the circuit (ignoring, once again, the transient effects during switching periods). This is in contrast to the dynamic circuit class, that relies on temporary storage of signal values on the capacitance of high-impedance circuit nodes. The latter approach has the advantage that the resulting gate is simpler and faster. On the other hand, its design and operation are more involved than those of its static counterpart, due to an increased sensitivity to noise.

Two I/P NAND gate in complementary Static CMOS Style

#### CMOS TRANSMISSION GATE:

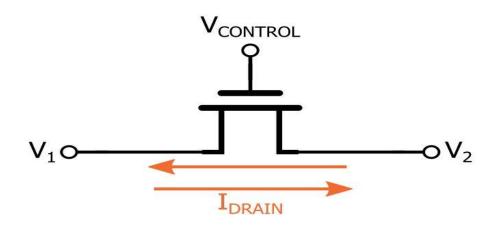

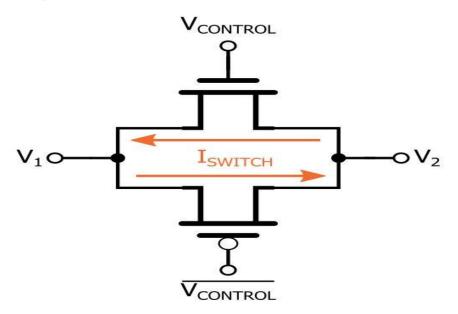

We usually see MOSFETs arranged with their sources and drains connected—either directly or through, for example, a resistor or active load—to positive and negative supply rails, with the gate acting as the input terminal. This is true in both analog circuits, such as the common-source amplifier, and digital circuits, such as the ubiquitous CMOS inverter. It's good to remember, though, that the MOSFET is not limited to configurations such as these.

The channel created by a sufficiently high gate-to-source voltage allows current to flow between the source and drain terminals, and in this sense the MOSFET is a voltage-controlled switch. Thus, there is no law that prevents us from using the source and drain as input and output terminals, with the control voltage applied to the gate.

A single NMOS (or PMOS) transistor can be used as a voltage-controlled switch. The "circuit" (really just a single transistor) is the following:

the arrow that usually identifies the source is removed. This is because the source terminal actually changes according to whether  $V_1$  is higher than  $V_2$  or  $V_2$  is higher than  $V_1$ . Also, the use of  $V_1$  and  $V_2$  instead of  $V_{IN}$  and  $V_{OUT}$  is intended to emphasize that this single NMOS transistor can indeed conduct current in both directions.

As probably expected, this circuit is far from a perfect switch. One problem is the source voltage: The current through the MOSFET is influenced by the source voltage, and the source voltage depends on whatever signal is passing through the switch. Indeed, if the gate is controlled by a driver that cannot exceed  $V_{DD}$ , the transistor can pass signals only as high as  $V_{DD}$  minus the threshold voltage. This threshold-voltage limitation is made even worse by the body effect, which comes into play when the FET's source and body terminals are not at the same potential.

When you analyze and ponder this switch, you recognize a certain asymmetry. For example, if we are using this switch for pass-transistor logic, the NMOS can effectively pass a logic-low signal but not a full logic-high signal. Is it possible to modify the circuit in a way that will redress this asymmetry? If you are maintaining a good CMOS mentality, your intuition might tell you that we could achieve better overall performance by incorporating a PMOS transistor to compensate for the deficiencies of the NMOS.

Here we have a PMOS in parallel with the NMOS; I used an "invert" circle to identify the PMOS transistor. Note that the control signal applied to the PMOS is the complement of the control signal applied to the NMOS; this is reminiscent of the CMOS inverter, where a logic-high voltage turns on the NMOS and a logic-low voltage turns on the PMOS.

This CMOS transmission gate is a synergistic system—the NMOS provides good switch performance under conditions that are favorable for itself but not for the PMOS, and the PMOS provides good switch performance under conditions that are favorable for itself but not for the NMOS. The result is a simple yet effective bidirectional voltage-controlled switch that is suitable for both analog and digital applications.

#### DOMINO LOGIC:

Properties of Domino Logic

- Only non-inverting logic can be implemented ‰

- Very high speed f

- static inverter can be skewed, only L-H transition critical f

- Input capacitance reduced smaller logical effort

#### **DESIGNING WITH DOMINO LOGIC:**

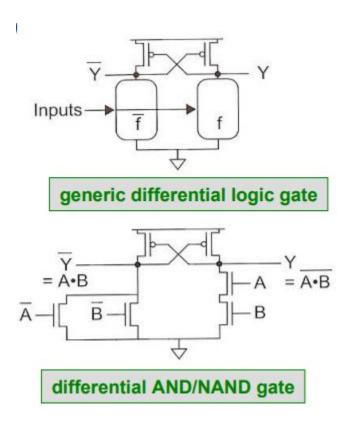

## DIFFERENTIAL CASCODE VOLTAGE SWITCH LOGIC:

- Performance advantage of ratioed circuits without the extra power

- Requires complementary inputs produces complementary outputs

$\bullet$  Operation – two nMOS arrays one for f, one for f – cross-coupled load pMOS – one path is always active

• since either f or f is always true – other path is turned off

• no static power generic differential logic gate differential AND/NAND gate (logic arrays turns off one load)

#### **Advantages of CVSL:**

low load capacitance on inputs no static power consumption automatic complementary functions

#### **Disadvantages:**

requires complementary inputs

more transistors for single function

## SCALING OF MOS TRANSISTOR:

#### **Types of Scaling**

Two types of scaling are common:

1) constant field scaling and

2) constant voltage scaling.

Constant field scaling yields the largest reduction in the power-delay product of a single transistor. However, it requires a reduction in the power supply voltage as one decreases the minimum feature size.

Constant voltage scaling does not have this problem and is therefore the preferred scaling method since it provides voltage compatibility with older circuit technologies. The disadvantage of constant voltage scaling is that the electric field increases as the minimum feature length is reduced. This leads to velocity saturation, mobility degradation, increased leakage currents and lower breakdown voltages. After scaling, the different Mosfet parameters will be converted as given by table below:

Before Scaling After Constant Field Scaling After Constant Voltage Scaling

|                  |                                             | 1                                                           |  |

|------------------|---------------------------------------------|-------------------------------------------------------------|--|

| Before Scaling   | After Constant Field Scaling                | After Constant Voltage Scaling                              |  |

| L                | L' = L/s                                    | L' = L/s                                                    |  |

| W                | W = W/s                                     | w' = W/s                                                    |  |

| t                | $t_{ox} = t_{ox}/s$                         | $t_{ox} = t_{ox}/s$                                         |  |

| Xi               | $x_i = x_i / s$                             | $x_i = x_i / s$                                             |  |

| Vdd              | $V_{DD} = V_{DD} / s$                       | $V_{DD} = V_{DD}$                                           |  |

| Vth              | $V_{Ih} = V_{Ih}/s$                         | $V_{Ih} = V_{Ih}$                                           |  |

| Na or N <b>d</b> | $N'_a = N_a * s \text{ or } N'_d = N_d * s$ | $N'_{a} = N_{a} * s^{2} \text{ or } N'_{d} = N_{d} * s^{2}$ |  |

| Cox              | $C'_{ox} = C_{ox} * s$                      | $C_{ox} = C_{ox} * s$                                       |  |

| IDS              | $I_{DS} = I_{DS} / s$                       | $I_{DS} = I_{DS} * s$                                       |  |

| PD               | $P_D' = P_D / s^2$                          | $P_D' = P_D * s$                                            |  |

Where  $\mathbf{s} =$  scaling parameter of MOS

# UNIT III

# **VLSI IMPLEMENTATION STRATEGIES**

## Design of Carry Lookahead Adders :

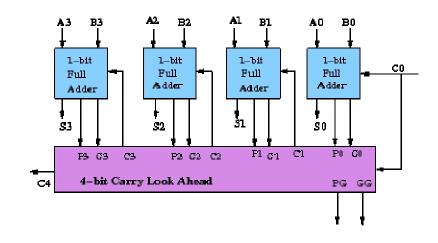

To reduce the computation time, there are faster ways to add two binary numbers by using carry lookahead adders. They work by creating two signals P and G known to be Carry Propagator and Carry Generator. The **carry propagator** is propagated to the next level whereas the **carry generator** is used to generate the output carry, regardless of input carry. The block diagram of a 4-bit Carry Lookahead Adder is shown here below -

The number of gate levels for the carry propagation can be found from the circuit of full adder. The signal from input carry Cin to output carry Cout requires an AND gate and an OR gate, which constitutes two gate levels. So if there are four full adders in the parallel adder, the output carry  $C_5$  would have 2 X 4 = 8 gate levels from  $C_1$  to  $C_5$ . For an n-bit parallel adder, there are 2n gate levels to propagate through.

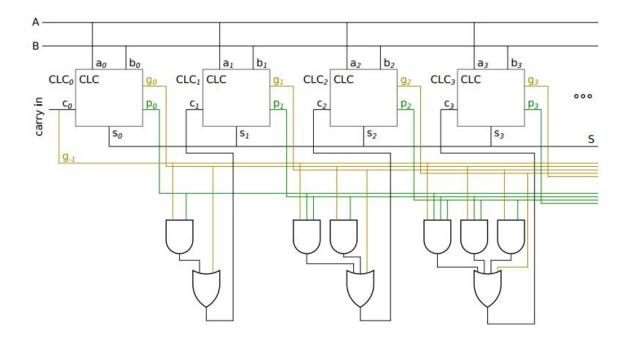

#### CARRY GENERATION LOGIC:

Types of carry generation logic (CGL): lookahead and ripple. With lookahead CGL adder above is a CLA. With ripple CGL adder above is equivalent to a ripple adder.

Boolean expressions for carry signals  $c_0$  to  $c_3$ :

- $c_0 = g_{-1}.$  $c_1 = g_{-1}p_0 + g_0.$

- $c_2 = g_{-1}p_0p_1 + g_0p_1 + g_1.$

$$c_3 = g_{-1}p_0p_1p_2 + g_0p_1p_2 + g_1p_2 + g_2.$$

Generalization of Lookahead Carry Generation

$$c_0 = g_{-1}.$$

$$c_1 = g_{-1}p_0 + g_0.$$

$$c_2 = g_{-1}p_0p_1 + g_0p_1 + g_1.$$

$$c_3 = g_{-1}p_0p_1p_2 + g_0p_1p_2 + g_1p_2 + g_2.$$

Generalizing we get

$$c_{i} = g_{-1}p_{0}p_{1}\cdots p_{i-1} + g_{0}p_{1}p_{2}\cdots p_{i-1} + g_{1}p_{2}p_{3}\cdots p_{i-1} + \cdots + g_{i-2}p_{i-1} + g_{i-1}$$

$$= \sum_{j=-1}^{i-1} g_{j} \prod_{k=j+1}^{i-1} p_{k}$$

The idea of delaying carry resolution until the end, or saving carries, is due to John von Neumann.<sup>[3]</sup>

Here is an example of a binary sum:

## 10111010101011011111000000001101

## + 110111101010110110111110111011111

Carry-save arithmetic works by abandoning the binary notation while still working to base 2. It computes the sum digit by digit, as

10111010101011011111000000001101

+ 1101111010101101101111110111011111

= 21122120202022022122111011102212

The notation is unconventional but the result is still unambiguous. Moreover, given n adders (here, n=32 full adders), the result can be calculated after propagating the inputs through a single adder, since each digit result does not depend on any of the others.

If the adder is required to add two numbers and produce a result, carry-save addition is useless, since the result still has to be converted back into binary and this still means that carries have to propagate from right to left. But in large-integer arithmetic, addition is a very rare operation, and adders are mostly used to accumulate partial sums in a multiplication.

## **CARRY SAVE ACCUMULATORS:**

The key to success is that at the moment of each partial addition we add three bits:

- 0 or 1, from the number we are adding.

- 0 if the digit in our store is 0 or 2, or 1 if it is 1 or 3.

- 0 if the digit to its right is 0 or 1, or 1 if it is 2 or 3.

To put it another way, we are taking a carry digit from the position on our right, and passing a carry digit to the left, just as in conventional addition; but the carry digit we pass to the left is the result of the *previous* calculation and not the current one. In each clock cycle, carries only have to move one step along, and not *n* steps as in conventional addition.

Because signals don't have to move as far, the clock can tick much faster.

There is still a need to convert the result to binary at the end of a calculation, which effectively just means letting the carries travel all the way through the number just as in a conventional adder. But if we have done 512 additions in the process of performing a 512-bit multiplication, the cost of that final conversion is effectively split across those 512 additions, so each addition bears 1/512 of the cost of that final "conventional" addition.

At each stage of a carry-save addition,

- 1. We know the result of the addition at once.

- 2. We *still do not know* whether the result of the addition is larger or smaller than a given number (for instance, we do not know whether it is positive or negative).

This latter point is a drawback when using carry-save adders to implement modular multiplication (multiplication followed by division, keeping the remainder only).

The carry-save unit consists of n <u>full adders</u>, each of which computes a single sum and carry bit based solely on the corresponding bits of the three input numbers. Given the three n - bit numbers **a**, **b**, and **c**, it produces a partial sum **ps** and a shift-carry **sc**:

$\label{eq:c_i} e_{i}=a_{i}\oplus b_{i}\oplus c_{i} \ b_{i}\ b_$

The entire sum can then be computed by:

1. <u>Shifting</u> the carry sequence **sc** left by one place.

2. Appending a 0 to the front (<u>most significant bit</u>) of the partial sum sequence **ps**.

3. Using a <u>ripple carry adder</u> to add these two together and produce the resulting n + 1-bit value.

## **MULTIPLIERS:**

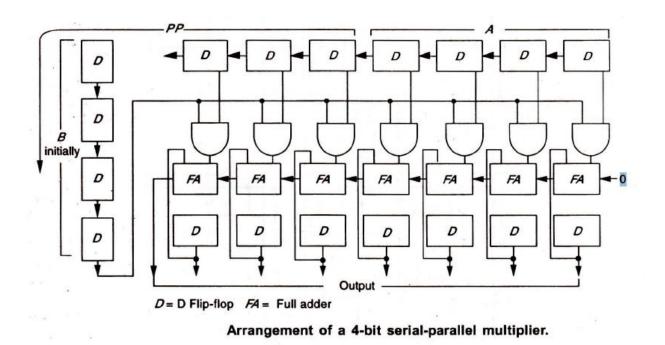

#### The Serial-parallel Multiplier

This multiplier is the simplest one, the multiplication being considered as a succession of additions.

If

$A = (a_n a_{n-1} a_{n-2} \dots a_0)$  and

$$B = (b_n b_{n-1} b_{n-2} \dots \dots \dots b_0)$$

then the product A.B may be expressed as

$A.B = (A.2^{n}.b_{n} + A.2^{n-1}.b_{n-1} + A.2^{n-2}.b_{n-2} \dots A.2^{0}.b_{0})$

A possible form of this adder for multiplying four-bit quantities, based on this expression, is set out in the below Figure. Note that D indicates a D flip-flop simple and FA indicates a full. adder--or adder bit slice. Number A is entered in the right-most 4-bits of the top row of D flip-flops which are connected to three further D flip-flops to form a 7-bit shift register to allow the multiplication of number A by  $2^1$ ,  $2^2 \dots 2^n$ , thus forming the *partial product* at each stage of the process.

The structure under discussion here is suited only to positive or unsigned operands. If the operands are negative and twos complement encoded, then:

1. The most significant bit of B will have a negative weight and so a subtraction must be performed as the last step.

2. The most significant bit of A must be replicated since operand A must be expanded to 2N bits.

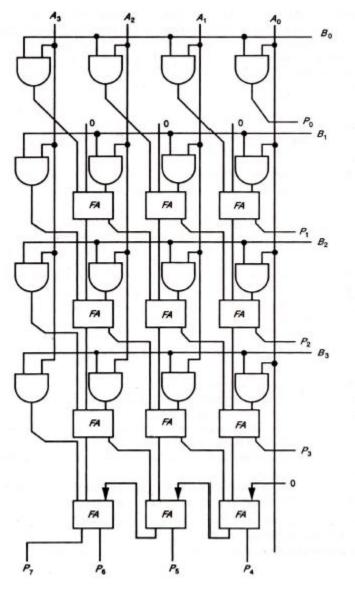

THE BRAUN ARRAY:

A relatively simple form of parallel adder is the Braun array . All partial products *A.bk* are computed in parallel, then collected through a cascaded array of carry save adders. At the bottom of the array, an adder is used to convert the carry save form to the required form of output. Completion time is fixed by the depth of the array, and by the carry propagation characteristics of the adder. Notice that this multiplier is suited only to positive operands. Negative operands can be handled, for example, by the Baugh-Wooley multiplier.

4 BIT Braun Multiplier.

## Twos Complement MultiplIcation Using the Baugh-Wooley Method

This technique has been developed to  $\cdot$  design multipliers that are regular in structure and suited for twos complement numbers.

Let us consider two numbers A and B:

$$A = (a_{n-1} \dots a_0) = -a_{n-1} \cdot 2^{n-1} + \sum_{0}^{n-2} a_i \cdot 2^i$$

$$B = (b_{n-1} \dots b_0) = -b_{n-1} \cdot 2^{n-1} + \sum_{0}^{n-2} b_i \cdot 2^i$$

The product A.B is given by:

$$A.B = a_{n-1}.b_{n-1}.2^{n-2} + \sum_{0}^{n-2} \sum_{0}^{n-2} a_i.b_j.2^{i+j} - a_{n-1} \sum_{0}^{n-2} b_i.2^{n+i-1} - b_{n-1} \sum_{0}^{n-2} a_i.2^{n+i-1}$$

If we use this form, it may be seen that subtraction operations are needed as well as addition. However, the negative terms may be rewritten, for example:

$$a_{n-1}\sum_{0}^{n-2}b_i \cdot 2^{n+i-1} = a_{n-1} \cdot \left(-2^{n-2} + 2^{n-1} + \sum_{0}^{n-2}\overline{b_i} \cdot 2^{n+i-1}\right)$$

Using this approach, A.B becomes

$$A.B = a_{n-1}.b_{n-1}.2^{n-2} + \sum_{0}^{n-2} \sum_{0}^{n-2} a_i.b_i.2^{i+j} + b_{n-1} \left( -2^{n-2} + 2^{n-1} + \sum_{0}^{n-2} \overline{a}_i.2^{n+i-1}_{\infty} \right) + a_{n-1} \left( -2^{n-2} + 2^{n-1} + \sum_{0}^{n-2} \overline{b}_i.2^{n+i-1} \right)$$

This equation may be put in a more convenient form by recognizing that

$$-(b^{n-1} + a^{n-1}) \cdot 2^{2n-2} = -2^{2n-1} + (\overline{a_{n-1}} + \overline{b_{n-1}}) \cdot 2^{2n-2}$$

Thus, AB is given by

$$A.B = 2^{2n-1} + (\overline{a_{n-1}} + \overline{b_{n-1}} + a^{n-1}.b^{n-1}).2^{2n-2}$$

$$+ \sum_{0}^{n-2} \sum_{0}^{n-2} a_i.b_j.2^{i+j} + (a_{n-1} + b_{n-1}).2^{n-1}$$

$$+ \sum_{0}^{n-2} b_{n-1}.\overline{a}_i.2^{n+1-j} + \sum_{0}^{n-2} a_{n-1}.\overline{b}_i.2^{n+i-1}$$

Since *A* and *B* are n-bit operands, their product may extend to 2n-bits. The first, most significant, bit is taken into account by the first term -22n-t which is fed to the multiplier as a 1 in the most significant cell. In serial-parallel multipliers there are as many idle clock cycles as there are Os in the multiplicand and the same situation applies in Braun and Baugh-Wooley arrays. For this reason, it may be useful to introduce pipelining concepts between successive lines of the

array. The clock speed of the pipeline is limited by the speed of the output adder, but it is possible to introduce further pipelining between the adder cells giving rise to the systolic array multiplier.

**FPGA**: A Field-Programmable Gate Array (FPGA) is a semiconductor device containing programmable logic components called "logic blocks", and programmable interconnects. Logic blocks can be programmed to perform the function of basic logic gates such as AND, and XOR, or more complex combinational functions such as decoders or mathematical functions. **ASIC**: An application-specific integrated circuit (ASIC) is an integrated circuit designed for a

particular use, rather than intended for general-purpose use. Processors, RAM, ROM, etc are examples of ASICs.

## **FPGA vs ASIC**

## Speed

ASIC rules out FPGA in terms of speed. As ASIC are designed for a specific application they can be optimized to maximum, hence we can have high speed in ASIC designs. ASIC can have hight speed clocks.

## Cost

FPGAs are cost effective for small applications. But when it comes to complex and large volume designs (like 32-bit processors) ASIC products are cheaper.

#### Size/Area

FPGA are contains lots of LUTs, and routing channels which are connected via bit streams(program). As they are made for general purpose and because of re-usability. They are ingeneral larger designs than corresponding ASIC design. For example, LUT gives you both registered and non-register output, but if we require only non-registered output, then its a waste of having a extra circuitry. In this way ASIC will be smaller in size.

## Power

FPGA designs consume more power than ASIC designs. As explained above the unwanted circuitry results wastage of power. FPGA wont allow us to have better power optimization. When it comes to ASIC designs we can optimize them to the fullest.

## Time to Market

FPGA designs will till less time, as the design cycle is small when compared to that of ASIC designs. No need of layouts, masks or other back-end processes. Its very simple: Specifications -- HDL + simulations -- Synthesis -- Place and Route (along with static-analysis) -- Dump code onto FPGA and Verify. When it comes to ASIC we have to do floor planning and also advanced verification. The FPGA design flow eliminates the complex and time-consuming floor planning, place and route, timing analysis, and mask / re-spin stages of the project since the design logic is already synthesized to be placed onto an already verified, characterized FPGA device.

## **Type of Design**

ASIC can have mixed-signal designs, or only analog designs. But it is not possible to design them using FPGA chips.

#### Customization

ASIC has the upper hand when comes to the customization. The device can be fully customized as ASICs will be designed according to a given specification. Just imagine implementing a 32-bit processor on a FPGA!

#### Prototyping

Because of re-usability of FPGAs, they are used as ASIC prototypes. ASIC design HDL code is first dumped onto a FPGA and tested for accurate results. Once the design is error free then it is taken for further steps. Its clear that FPGA may be needed for designing an ASIC.

## Non Recurring Engineering/Expenses

NRE refers to the one-time cost of researching, designing, and testing a new product, which is generally associated with ASICs. No such thing is associated with FPGA. Hence FPGA designs are cost effective.

## Simpler Design Cycle

Due to software that handles much of the routing, placement, and timing, FPGA designs have smaller designed cycle than ASICs.

## More Predictable Project Cycle

Due to elimination of potential re-spins, wafer capacities, etc. FPGA designs have better project cycle.

## Tools

Tools which are used for FPGA designs are relatively cheaper than ASIC designs.

## **Re-Usability**

A single FPGA can be used for various applications, by simply reprogramming it (dumping new HDL code). By definition ASIC are application specific cannot be reused.

## Field-Programmable Gate Array

In most FPGAs, the logic blocks also include memory elements, which may be simple flip-flops or more complete blocks of memory.

#### Applications

ASIC prototyping: Due to high cost of ASIC chips, the logic of the application is first verified by dumping HDL code in a FPGA. This helps for faster and cheaper testing. Once the logic is verified then they are made into ASICs.

- Very useful in applications that can make use of the massive parallelism offered by their architecture. Example: code breaking, in particular brute-force attack, of cryptographic algorithms.

- FPGAs are sued for computational kernels such as FFT or Convolution instead of a microprocessor.

- Applications include digital signal processing, software-defined radio, aerospace and defense systems, medical imaging, computer vision, speech recognition, cryptography, bio-informatics, computer hardware emulation and a growing range of other areas.

#### Architecture

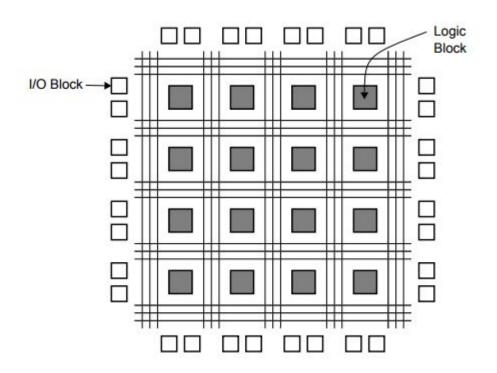

FPGA consists of large number of "configurable logic blocks" (CLBs) and routing channels. Multiple I/O pads may fit into the height of one row or the width of one column in the array. In general all the routing channels have the same width. The block diagram of FPGA architecture is shown below.

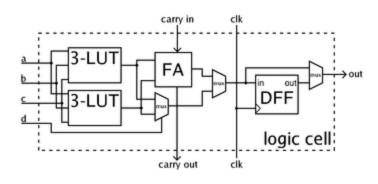

**CLB**: The CLB consists of an n-bit look-up table (LUT), a flip-flop and a 2x1 mux. The value n is manufacturer specific. Increase in n value can increase the performance of a FPGA. Typically n is 4. An n-bit lookup table can be implemented with a multiplexer whose select lines are the inputs of the LUT and whose inputs are constants. An n-bit LUT can encode any n-input Boolean function

by modeling such functions as truth tables. This is an efficient way of encoding Boolean logic functions, and LUTs with 4-6 bits of input are in fact the key component of modern FPGAs. The block diagram of a CLB is shown below.

Each CLB has n-inputs and only one input, which can be either the registered or the unregistered LUT output. The output is selected using a 2x1 mux. The LUT output is registered using the flip-flop (generally D flip-flop). The clock is given to the flip-flop, using which the output is registered. In general, high fanout signals like clock signals are routed via special-purpose dedicated routing networks, they and other signals are managed separately.

Routing channels are programmed to connect various CLBs. The connecting done according to the design. The CLBs are connected in such a way that logic of the design is achieved.

#### **FPGA Programming**

The design is first coded in HDL (Verilog or VHDL), once the code is validated (simulated and synthesized). During synthesis, typically done using tools like Xilinx ISE, FPGA Advantage, etc, a technology-mapped net list is generated. The net list can then be fitted to the actual FPGA architecture using a process called place-and-route, usually performed by the FPGA company's proprietary place-and-route software. The user will validate the map, place and route results via timing analysis, simulation, and other verification methodologies. Once the design and validation process is complete, the binary file generated is used to (re)configure the FPGA. Once the FPGA is (re)configured, it is tested. If there are any issues or modifications, the original HDL code will be modified and then entire process is repeated, and FPGA is reconfigured.

#### FULL CUSTOM DESIGN:

• A Full custom design is one which includes some (possibly all) logic cells that are customized and all mask layers that are customized.

- A microprocessor is an example of a full-custom IC. Designers spend many hours squeezing the most out of every last square micron of microprocessor chip space by hand.

- Customizing all of the IC features in this way allows designers to include analog circuits, optimized memory cells, or mechanical structures on an IC, for example. Full-custom ICs are the most expensive to manufacture and to design.

- The manufacturing lead time (the time required just to make an IC not including design time) is typically eight weeks for a full-custom IC.

- These specialized full-custom ICs are often intended for a specific application so, we might call some of them as full-custom ASICs

- In a full-custom design One has to use full-custom design if the technology is new or so specialized that there are no existing cell libraries or because the technology is so specialized that some circuits must be custom designed.

- Fewer and fewer full-custom ICs are being designed because of the problems with these special parts of the technology.

- The growing member of this family, now a days is the mixed analog/digital design,

- an engineer designs some or all of the logic cells, circuits, or layout specifically for one application. This means the designer avoids using pretested and pre characterized cells for all or part of that design.

- This might be because existing cell libraries are not fast enough, or the logic cells are not small enough or consume too much power.

#### SEMI CUSTOM DESIGN:

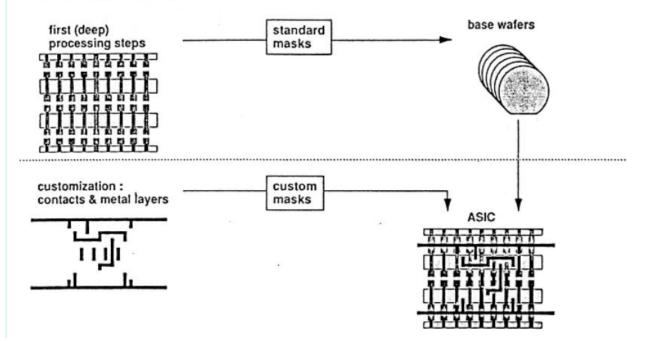

## GATE ARRAY BASED DESIGN:

In view of the fast prototyping capability, the gate array (GA) comes after the FPGA.

Design implementation of

•FPGA chip is done with user programming,

- Gate array is done with metal mask design and processing.

- Gate array implementation requires a two-step manufacturing process:

a) The first phase, which is based on generic (standard) masks, results in an array of uncommitted transistors on each GA chip.

b) These uncommitted chips can be customized later, which is completed by defining the metal interconnects between the transistors of the array.

#### two-step manufacture :

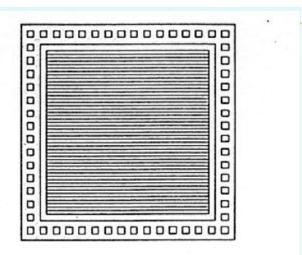

#### CHANNELLED VS CHANNEL- LESS (SOG) APPROACHES:

| 000000000000000000000000000000000000000 |  |

|-----------------------------------------|--|

|                                         |  |

|                                         |  |

|                                         |  |

|                                         |  |

|                                         |  |

routing problem is simpler OK with only one metal

flexibility in channel definition (position & width) over-the-cell routing higher packing density RAM-compatible supports variable-height cells & macrocells now universally used

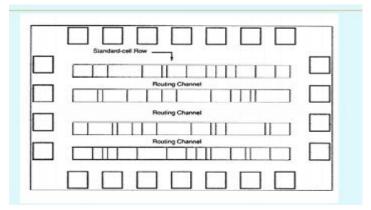

#### STANDARD CELL BASED DESIGN:

Each cell is designed with a fixed height.

- To enable automated placement of the cells, and

- Routing of inter-cell connections.